- Software - Simulation

- Software

- Aeronautic software

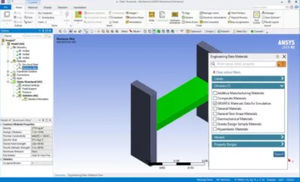

- ANSYS FRANCE SAS

- Products

- Catalogs

- News & Trends

- Exhibitions

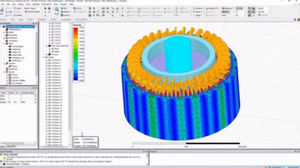

Analysis software designfor aeronautics

Add to favorites

Compare this product

fo_shop_gate_exact_title

Characteristics

- Function

- analysis, design

- Applications

- for aeronautics

Description

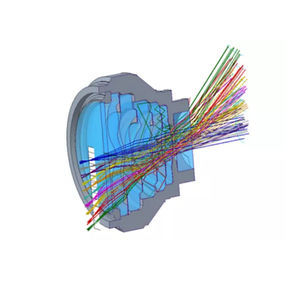

Ansys medini analyze supports key safety analysis methods at various levels of a chip, ranging from IP Design of integrated components, up to SoCs and electronic boards.

Semiconductor Analysis Integrated With Overall Systems Analysis

Ansys medini analyze supports best-practice workflows that graphically link specific areas of the semiconductor design to key functions within the electronics architecture. This allows engineers to analyze and address potential failure modes as they verify the functional safety of semiconductor components. Engineers can efficiently and consistently execute the safety-related activities such as the FMEDA, required by safety standards like ISO 26262: 2018 part 11.

Failure Rate Prediction

Map Chip Design to Functions

Failure Mode Effect and Diagnostic Analysis

Digital and Analog Chip Analysis

Quick Specs

Streamline and automate functional safety analysis across the entire electronics architecture — including down to the chip level. Any inconsistencies in the functional safety analysis are eliminated, and confirmation reviews and assessments are accelerated.

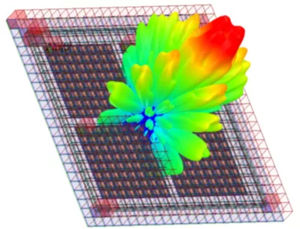

Failure Rate Distribution by Die Area

Requirement Traceability

IP Design Import

Determine and Analyze Potential Failure Modes

FMEDA

Safety Mechanism Design

Map Blocks of the Semiconductor Design to System Functions

Transient Failure Analysis

Diagnostic Coverage Analysis

Catalogs

No catalogs are available for this product.

See all of ANSYS FRANCE SAS‘s catalogsExhibitions

Meet this supplier at the following exhibition(s):

*Prices are pre-tax. They exclude delivery charges and customs duties and do not include additional charges for installation or activation options. Prices are indicative only and may vary by country, with changes to the cost of raw materials and exchange rates.