- Software - Simulación

- Software

- Software para la aeronáutica

- ANSYS FRANCE SAS

Software de análisis de diseñopara la aeronáutica

Añadir a mis favoritos

Añadir al comparador

Características

- Función

- de análisis, de diseño

- Aplicaciones

- para la aeronáutica

Descripción

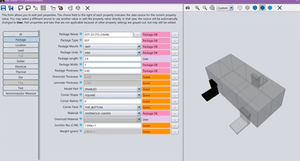

Ansys medini analyze admite métodos clave de análisis de seguridad en varios niveles de un chip, desde el diseño IP de componentes integrados, hasta SoC y placas electrónicas.

Análisis de semiconductores integrado con el análisis global de sistemas

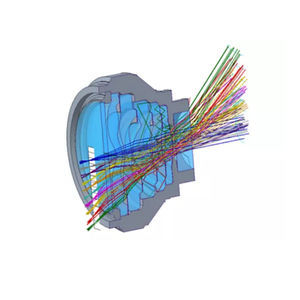

Ansys medini analyze admite flujos de trabajo de mejores prácticas que vinculan gráficamente áreas específicas del diseño del semiconductor con funciones clave dentro de la arquitectura electrónica. Esto permite a los ingenieros analizar y abordar posibles modos de fallo mientras verifican la seguridad funcional de los componentes semiconductores. Los ingenieros pueden ejecutar de forma eficiente y coherente las actividades relacionadas con la seguridad, como la FMEDA, exigidas por normas de seguridad como la ISO 26262: 2018 parte 11.

Predicción de la tasa de fallos

Asignación del diseño del chip a las funciones

Análisis de modos de fallo, efectos y diagnóstico

Análisis de chips digitales y analógicos

Especificaciones rápidas

Agilice y automatice el análisis de seguridad funcional en toda la arquitectura electrónica, incluido el nivel de chip. Se elimina cualquier incoherencia en el análisis de seguridad funcional y se aceleran las revisiones y evaluaciones de confirmación.

Distribución de la tasa de fallos por área del chip

Trazabilidad de requisitos

Importación de diseños IP

Determinación y análisis de posibles modos de fallo

FMEDA

Diseño de mecanismos de seguridad

Asignación de bloques del diseño del semiconductor a las funciones del sistema

Análisis de fallos transitorios

Análisis de cobertura de diagnóstico

---

Catálogos

No hay ningún catálogo disponible para este producto.

Ver todos los catálogos de ANSYS FRANCE SAS* Los precios no incluyen impuestos, gastos de entrega ni derechos de exportación. Tampoco incluyen gastos de instalación o de puesta en marcha. Los precios se dan a título indicativo y pueden cambiar en función del país, del coste de las materias primas y de los tipos de cambio.